| کد مقاله | کد نشریه | سال انتشار | مقاله انگلیسی | نسخه تمام متن |

|---|---|---|---|---|

| 713900 | 892177 | 2013 | 6 صفحه PDF | دانلود رایگان |

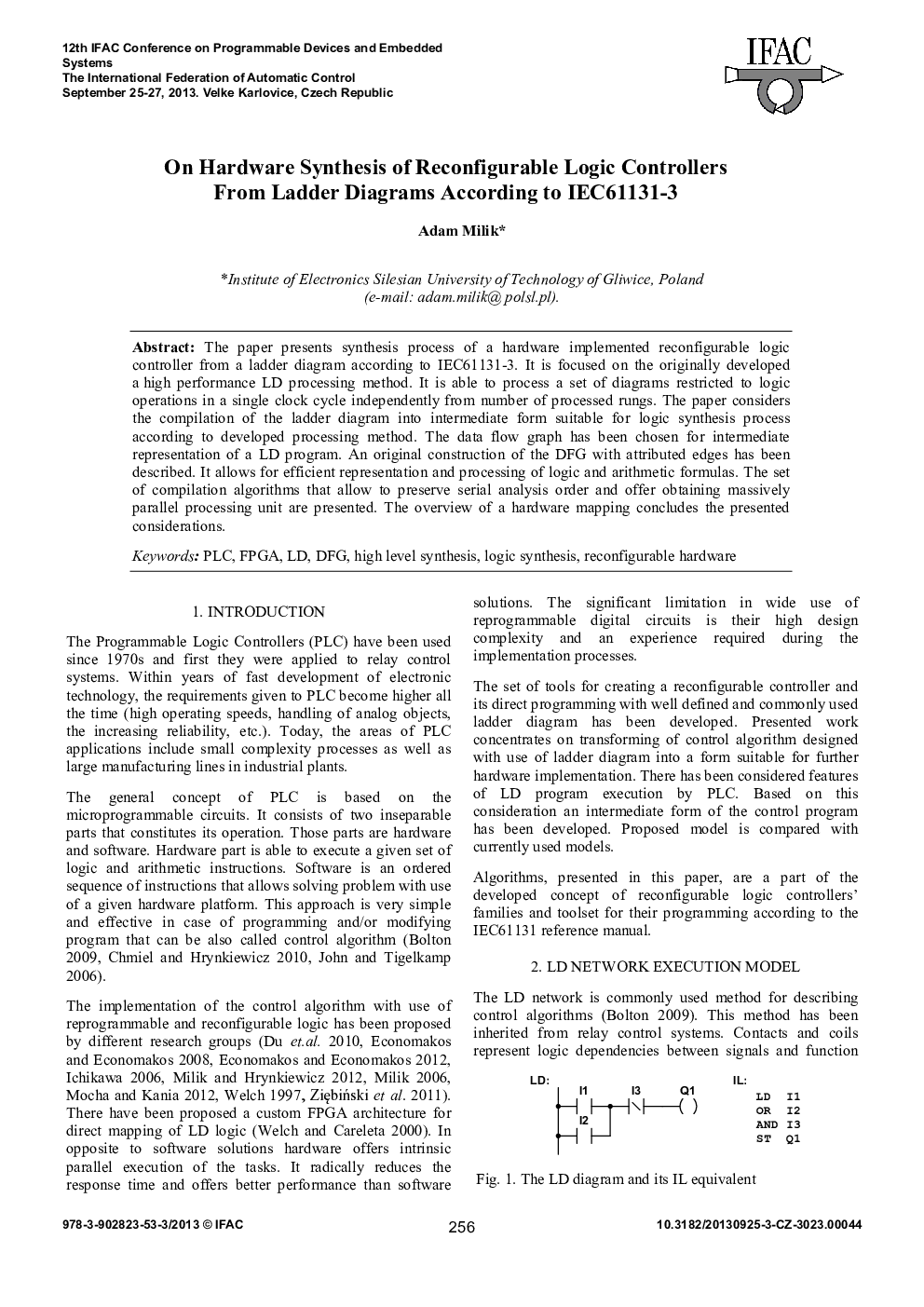

The paper presents synthesis process of a hardware implemented reconfigurable logic controller from a ladder diagram according to IEC61131-3. It is focused on the originally developed a high performance LD processing method. It is able to process a set of diagrams restricted to logic operations in a single clock cycle independently from number of processed rungs. The paper considers the compilation of the ladder diagram into intermediate form suitable for logic synthesis process according to developed processing method. The data flow graph has been chosen for intermediate representation of a LD program. An original construction of the DFG with attributed edges has been described. It allows for efficient representation and processing of logic and arithmetic formulas. The set of compilation algorithms that allow to preserve serial analysis order and offer obtaining massively parallel processing unit are presented. The overview of a hardware mapping concludes the presented considerations.

Journal: IFAC Proceedings Volumes - Volume 46, Issue 28, 2013, Pages 256-261