| کد مقاله | کد نشریه | سال انتشار | مقاله انگلیسی | نسخه تمام متن |

|---|---|---|---|---|

| 712768 | 892157 | 2015 | 6 صفحه PDF | دانلود رایگان |

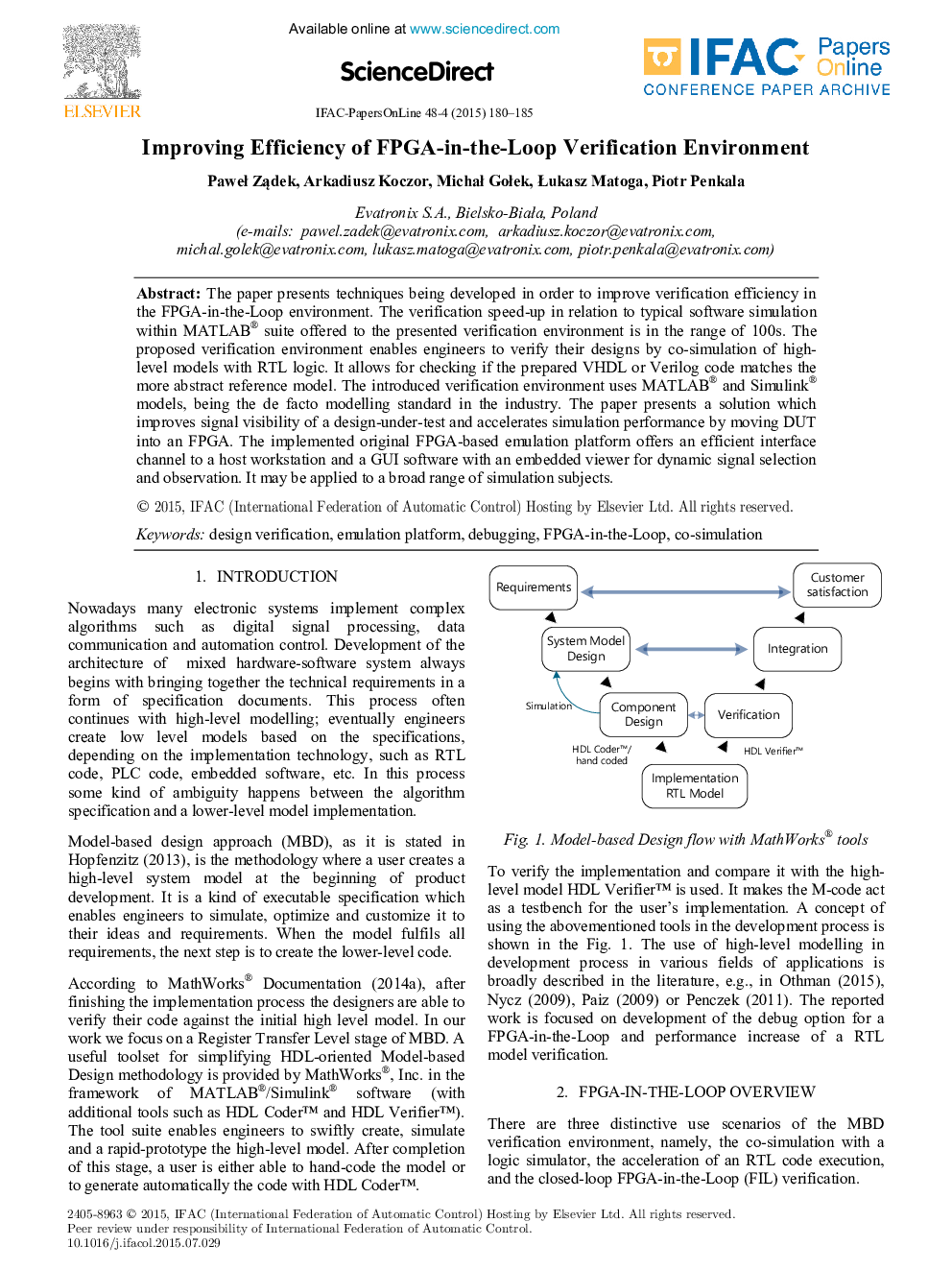

The paper presents techniques being developed in order to improve verification efficiency in the FPGA-in-the-Loop environment. The verification speed-up in relation to typical software simulation within MATLAB® suite offered to the presented verification environment is in the range of 100s. The proposed verification environment enables engineers to verify their designs by co-simulation of high- level models with RTL logic. It allows for checking if the prepared VHDL or Verilog code matches the more abstract reference model. The introduced verification environment uses MATLAB® and Simulink® models, being the de facto modelling standard in the industry. The paper presents a solution which improves signal visibility of a design-under-test and accelerates simulation performance by moving DUT into an FPGA. The implemented original FPGA-based emulation platform offers an efficient interface channel to a host workstation and a GUI software with an embedded viewer for dynamic signal selection and observation. It may be applied to a broad range of simulation subjects.

Journal: IFAC-PapersOnLine - Volume 48, Issue 4, 2015, Pages 180-185